# Color Computer 1/2/3 Hardware Programming

Chris Lomont, Aug 2007, version 0.82

This document collects and details hardware programming information for the TRS-80 Color Computer, versions 1, 2, and 3. Although it has some tutorial information in it, it is designed to be a reference. Many areas also apply to the Color Computer Clones such as the British Dragon 32/64.

It is compiled and edited by Chris Lomont, <u>www.lomont.org</u>. Send comments, corrections, and errors to CoCo3 at the above domain. Please don't repost this on the web, but point to this copy, so eventually all information is corrected and integrated.

This document is compiled from many sources, listed in the <u>Bibliography</u>. If you feel this infringes any of your copyrighted material, email me with your material, and I will remove or rewrite from scratch the offending sections.

Hex numbers start with a \$, as in 255=\$FF. Addresses like \$FFFE (65534) give the decimal in parentheses. 16-bit addresses like \$B0F1 are in 6809 CPU address space. On the Color Computer 3, 20-bit addresses like \$70FFF are in <u>GIME</u> address space. Also on the Color Computer 3, the <u>Memory Mapping Unit (MMU)</u> maps eight 8K pages from the <u>GIME</u> space into CPU space.

Many sections (marked TODO) need a lot more work, which I will do given time.

DISCLAIMER: All information provided as is, etc. Use at your own risk.

| Version History |           |                                                  |

|-----------------|-----------|--------------------------------------------------|

| 0.8             | June 2006 | Initial version and organization of material.    |

| 0.81            | July 2007 | One pass of cleanup and some new material added. |

| 0.82            | Aug 2007  | Rewrite, reformat, complete overhaul.            |

# Table of Contents

| COLOR COMPUTER 1/2/3 HARDWARE PROGRAMMING                                                                                                    | 1  |

|----------------------------------------------------------------------------------------------------------------------------------------------|----|

| TABLE OF CONTENTS                                                                                                                            | 2  |

| HARDWARE INTRODUCTION                                                                                                                        | 5  |

| 6809 CPU NOTES                                                                                                                               | 5  |

| COLOR COMPUTER 1/2 HARDWARE TOPICS (PIA, VDG, SAM)                                                                                           | 7  |

| PIA (Peripheral Interface Adapters)<br>VDG (Video Display Generator)<br>SAM (Synchronous Address Multiplexer)                                | 7  |

| COLOR COMPUTER 3 HARDWARE TOPICS (GIME)                                                                                                      | 9  |

| GIME (GRAPHICS INTERRUPT MEMORY ENHANCEMENT)<br>MMU (Memory Management Unit)<br>Graphics<br>Palettes<br>Interrupts<br>CoCo 1/2 compatibility |    |

| MEMORY MAPPING                                                                                                                               |    |

| CoCo 1/2:<br>CoCo 2 memory map<br>CoCo 3<br>Simple CoCo 3 Memory Map                                                                         |    |

| COLORS                                                                                                                                       | 14 |

| CoCo 1/2:<br>CoCo 3:                                                                                                                         |    |

| GRAPHICS MODES                                                                                                                               |    |

| CoCo 1/2<br>CoCo 3                                                                                                                           |    |

| TEXT MODES                                                                                                                                   |    |

| CoCo 1/2<br>CoCo 3                                                                                                                           |    |

| KEYBOARD                                                                                                                                     | 21 |

| JOYSTICK                                                                                                                                     | 22 |

| MOUSE                                                                                                                                        | 23 |

| INTERRUPTS                                                                                                                                   | 23 |

| CoCo 1/2/3<br>CoCo 3                                                                                                                         |    |

| SOUND                                                                                                                                        | 25 |

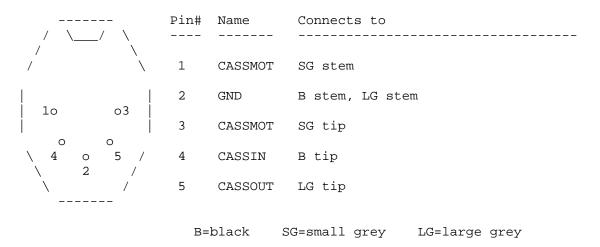

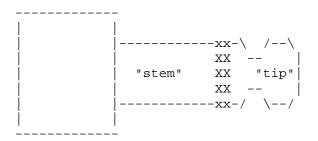

| CASSETTE STORAGE                                                                                                                             | 25 |

| File format<br>Hardware                                                                                                                      |    |

| DISK STORAGE                                                                                                                                 |    |

| DISK FORMAT                                                                                                   |    |

|---------------------------------------------------------------------------------------------------------------|----|

| CONTROLLER                                                                                                    |    |

| DUP - MERGE AND REMOVE                                                                                        |    |

| SERIAL I/O                                                                                                    |    |

| Software                                                                                                      | 25 |

| SOFTWARE                                                                                                      |    |

|                                                                                                               |    |

| CARTRIDGE INFO                                                                                                |    |

| BASIC, EXTENDED BASIC, AND DISK BASIC SUMMARY                                                                 |    |

| COLOR BASIC (NON-EXTENDED) SUMMARY                                                                            |    |

| EXTENDED COLOR BASIC SUMMARY                                                                                  |    |

| DISK BASIC SUMMARY                                                                                            |    |

| ROM ROUTINES                                                                                                  |    |

| Color Basic Info                                                                                              |    |

| Extended Color Basic Info                                                                                     |    |

| DISK COLOR BASIC INFO                                                                                         |    |

| Rom Routines                                                                                                  |    |

|                                                                                                               |    |

| COLOR COMPUTER HARDWARE REGISTER REFERENCE (\$FF00-\$FFFF)                                                    |    |

| PIA REFERENCE (\$FF00-\$FF3F)                                                                                 |    |

| PIA0 (\$FF00-\$FF1F)                                                                                          |    |

| PIA1 (\$FF20-\$FF3F)                                                                                          |    |

| DISK CONTROLLER REFERENCE                                                                                     |    |

| Disk Controller (\$FF40)                                                                                      |    |

| DSKREG Copies (\$FF41-\$FF47) (65345-65351)                                                                   |    |

| Status/Command (\$FF48)                                                                                       |    |

| Track \$FF49                                                                                                  |    |

| Sector \$FF4A                                                                                                 |    |

| Data \$FF4B                                                                                                   |    |

| Other Disks \$FF50-\$FF5F                                                                                     |    |

| MISCELLANEOUS HARDWARE                                                                                        |    |

| \$FF60 (65376)-\$FF62 (65378) X-Pad interface                                                                 |    |

| \$FF60 (65376)-\$FF67 (65383) CoCo Max A/D Module                                                             |    |

| \$FF60 (65376)-\$FF7F (65407) TC^3 SCSI                                                                       |    |

| \$FF63 (65379)-\$FF67 (65383) Unused                                                                          |    |

| \$FF68 (65384)-\$FF6B (65387) RS-232 PROGRAM PAK Interface                                                    |    |

| \$FF6C (65388)-\$FF6F (65391) Direct Connect Modem Pak                                                        |    |

| \$FF70 (65392),\$FF72 (65394) Musica stereo pack                                                              |    |

| \$FF70 (65392)-\$FF72 (65394) Laser light show D/A                                                            |    |

| \$FF70 (65392)-\$FF74 (65396) SPEECH SYSTEMS SUPERVOICE                                                       |    |

| \$FF70 (65392)-\$FF74 (65396) Burke & Burke CYBERVOICE                                                        |    |

| \$FF70 (65392)-\$FF78 (65400) Glenside IDE controller                                                         |    |

| \$FF7A (65392)-\$FF7B (65404) Orchestra-90                                                                    |    |

| \$FF7D (65405)-\$FF7E (65406) SOUND/SPEECH CARTRIDGE                                                          |    |

| \$FF7F(65407) MULTI-PAK PROGRAMMING REGISTER                                                                  |    |

| CoCo 3 GIME HARDWARE REFERENCE<br>\$FF90 (65424) Initialization Register 0 - INITO                            |    |

|                                                                                                               |    |

| \$FF91 (65425) Initialization Register 1 - INIT1<br>\$FF92 (65426) Interrupt Request Enable Register – IRQENR |    |

|                                                                                                               |    |

| \$FF93 (65427) Fast Interrupt Request Enable Reg - FIRQENR<br>\$FF94-\$FF95 TIMERMSB/TIMERLSB                 |    |

| \$FF94-\$FF95 11MERMSB/11MERLSB<br>\$FF96-\$FF97 - Unused                                                     |    |

| \$FF90-\$FF97 - Unusea<br>\$FF98 (65432) Video mode register - VMODE                                          |    |

|                                                                                                               |    |

| \$FF99 (65433) Video resolution register - VRES                | . 64 |

|----------------------------------------------------------------|------|

| \$FF9A (65434) Border color register - BRDR                    | . 66 |

| \$FF9C (65436) Vertical scroll register - VSC                  | . 66 |

| \$FF9D-\$FF9E Vertical offset register                         | . 66 |

| \$FF9F (65439) Horizontal offset register                      |      |

| \$FFA0-\$FFAF (65440-65455) MMU bank registers (tasks 0 and 1) |      |

| \$FFB0-\$FFBF (65456-65471) Color palette registers            |      |

| SAM REGISTERS \$FFC0-\$FFDF                                    |      |

| \$FFC0 (65472)-\$FFC5 (65477) SAM Video Display - SAM_Vx       |      |

| \$FFC6 (65478)-\$FFD3 (65491) SAM Page Select Reg-SAM_Fx       |      |

| \$FFD4 (65492)-\$FFD5 (65493) SAM Page Select Reg-SAMPAG       |      |

| \$FFD6 (65494)-\$FFD9 (65497) Clock Speed R0/R1 - SAM_R0/1     |      |

| \$FFDA (65498)-\$FFDD (65501) Memory size M0/M1 - SAM_M0/1     |      |

| \$FFDE/\$FFDF (65502/65503) ROM/RAM map type - SAM_TYP         |      |

| INTERRUPT VECTORS                                              | .73  |

| \$FFE0-\$FFF1 (65504/65522) Reserved                           | . 73 |

| \$FFF2-\$FFFF (65523/65535) Interrupt vectors                  | . 73 |

| COCO 3 DETAILED MEMORY MAP                                     | .74  |

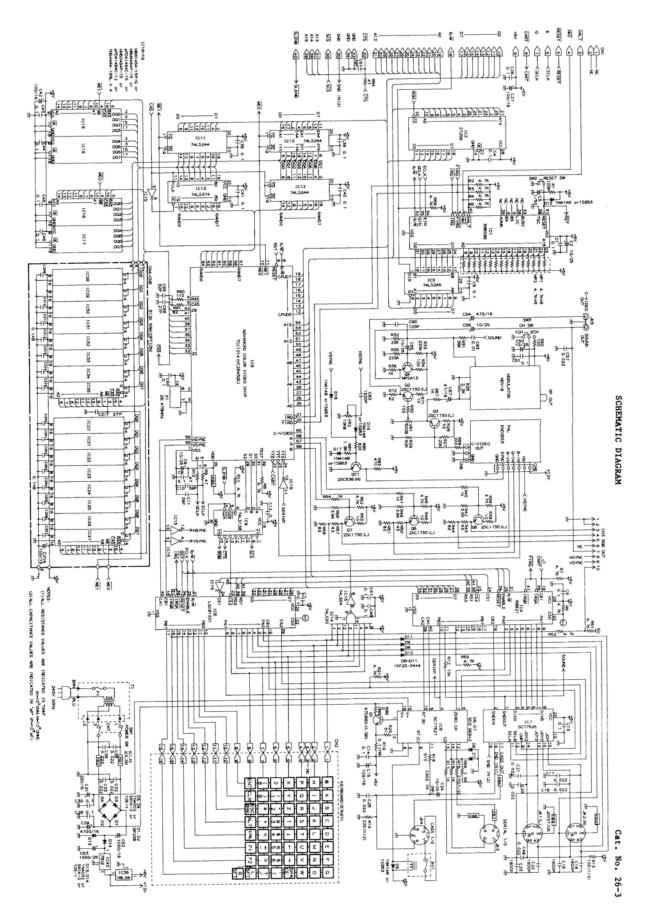

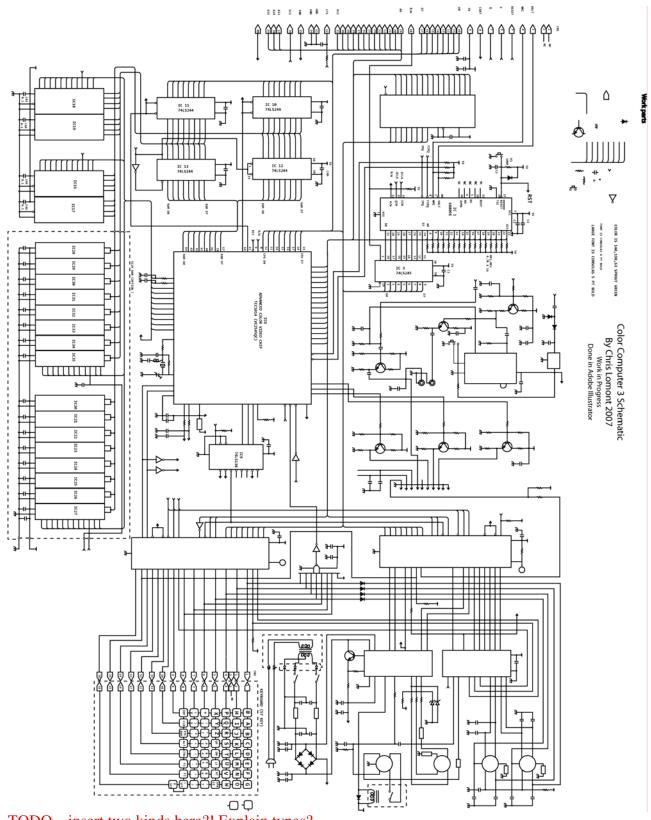

| SCHEMATICS                                                     | . 81 |

| BIBLIOGRAPHY                                                   | . 84 |

| GLOSSARY                                                       | . 84 |

| INDEX                                                          | . 84 |

| TODO                                                           | . 85 |

# **Hardware Introduction**

This document covers the hardware in the Color Computer, versions 1, 2, and 3, often called the CoCo 1, CoCo 2, and CoCo 3.

The original version of the Color Computer, the CoCo 1, was in a silver-gray case with a chiclet keyboard, and was available with a memory sizes of 4K (26-3001<sup>1</sup>), 16K (26-3002), or 32K (26-3003). Many actually had 64K of RAM, which could be accessed with special utilities. The second generation CoCo 2 came in 16K (standard and extended BASIC) and 64K RAM sizes, removed the 12V power line, and the new BASIC ROMs fixed some bugs. The CoCo 3 was a major upgrade using the ASIC Graphics Interrupt Memory Enhancement (GIME) chip, which added many new features, detailed below. Some of the new features included up to 512K of RAM, lowercase letters, 40 and 80 column text, higher clock speeds, new interrupt sources, and many new video modes.

TODO – pics?

The CoCo3 supports the CoCo 1 and 2 hardware in CoCo 1/2 compatibility mode, described in the CoCo 1/2 Compatibility Section.

All three versions of the CoCo run on a Motorola 6809 chip, details of which are in a different document. A brief note about the 6809 is <u>below</u>.

The main hardware interfaces are:

CoCo 1/2/3:General hardware Input/OutputPIAPeripheral Interface AdapterGeneral hardware Input/OutputSAMSynchronous Address MultiplexerDetermines how data movesVDGVideo Display GeneratorConverts RAM to images

CoCo 3 only:

<u>GIME</u> Graphics Interrupt Memory Enhancement What it says...

Miscellaneous hardware items cover disk drives, cassette, sound, joysticks, speech packs, modem packs, multi-pak, and more.

# 6809 CPU Notes

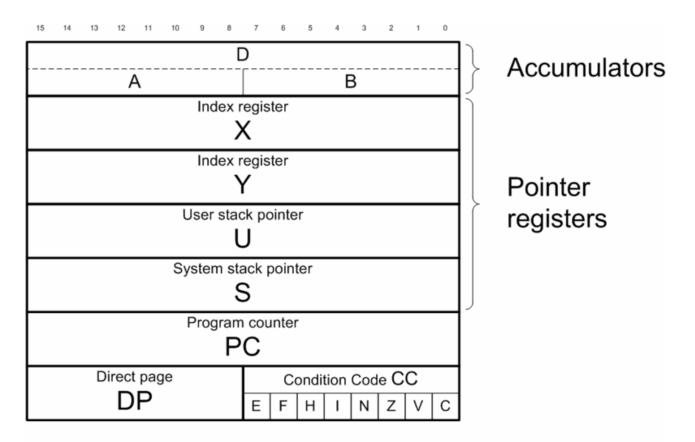

The Motorola 6809 is an 8-bit CPU with some 16-bit instructions and registers. Here is a rough picture of the programming model:

<sup>&</sup>lt;sup>1</sup> These type of numbers are from Radio Shack catalogs.

# 6809 Internal Registers

The condition code bits in the Condition Code register are used in this document, and are

| Bit | Function                                                                                    |  |

|-----|---------------------------------------------------------------------------------------------|--|

| Е   | During interrupt, if 1, indicated all registers on stack, else only PC and CC. Needed for R |  |

| 2   | (Return From Interrupt) opcode.                                                             |  |

| F   | FIRQ Disabled if 1. Set to 1 on power up and during interrupt processing.                   |  |

| Η   | Half Carry from low nibble to high nibble, used for DAA (Decimal Addition Adjust)           |  |

|     | opcode.                                                                                     |  |

| Ι   | IRQ Disabled if 1. Set to 1 on power up and during interrupt processing.                    |  |

| Ν   | Last operation resulted in Negative.                                                        |  |

| Ζ   | Last operation resulted in Zero.                                                            |  |

| V   | Signed arithmetic overflow.                                                                 |  |

| С   | Carry generated.                                                                            |  |

Many hobbyists have replaced the 6809 with the pin compatible Hitachi 6309EP, which offers higher performance, more registers, and many more opcodes. For details on the 6809 and 6309 see <a href="http://www.lomont.org/Software/Misc/CoCo/Lomont\_6809.pdf">http://www.lomont.org/Software/Misc/CoCo/Lomont\_6809.pdf</a>.

# Color Computer 1/2 Hardware Topics (PIA, VDG, SAM)

The main hardware interfaces in the CoCo 1 and 2 (also in the CoCo 3) are the 2 PIAs (Peripheral Interface Adapter), a SAM (Synchronous Address Multiplexer) and a VDG (Video Display Generator). Details follow.

The CoCo 1 came in 4K, 16K, and 32K RAM versions, with RAM starting at address \$0000 and going through \$1FFF, \$3FFF, and \$7FFF respectively. ROM addresses are \$8000-\$FFFF, with addresses \$FF00-\$FFFF being hardware access ports.

The CoCo 2 came with 64K of RAM, and 32K of ROM. The upper 32K was selected to be RAM or ROM by setting a bit in <u>\$FFDE/\$FFDF</u>.

The CoCo 2 has a RAM/ROM mode, and an all RAM mode, selected by SAM control bit TY, accessed from <u>\$FFDE/\$FFDF</u>.

32K RAM \$0000-\$7FFF /32K ROM \$8000-\$FFFF or 64K RAM \$0000-\$FFFF (TODO - vectors?)

All 3 CoCos have hardware interface registers in the 256 bytes from <u>\$FF00-\$FFFF</u>.

## PIA (Peripheral Interface Adapters)

The <u>PIA</u> is a Motorola MC6821 or MC6822. There are two PIA chips, PIA0 and PIA1, each consisting of 4 addresses. Each PIA has two data registers and two control registers.

PIA0 uses addresses \$FF00-\$FF03. Data registers \$FF00 and \$FF02 are mostly keyboard and printer interfaces, and control registers \$FF01 and \$FF03 handle horizontal and vertical sync interrupts and joystick direction.

PIA1 uses addresses \$FF20-\$FF23, handling cassette, printer, CoCo 1/2 video modes, audio, and cartridge info. Details are in the hardware section under the respective addresses.

### TODO

## VDG (Video Display Generator)

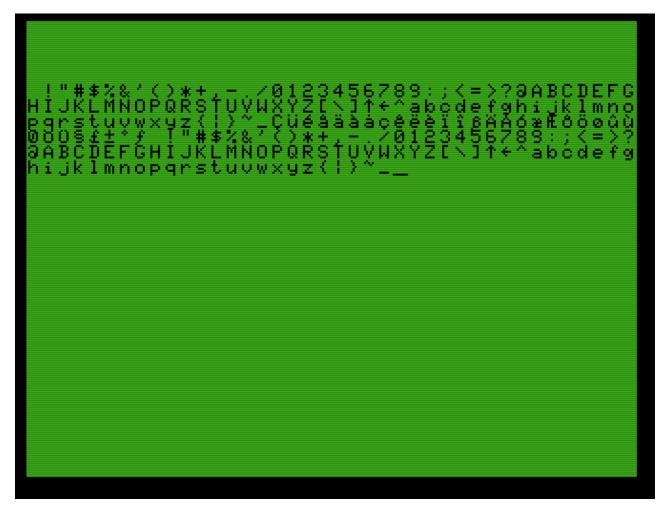

The VDG is a Motorola MC6847 (later, the enhanced MC6847T1), capable of displaying text and graphics contained within a roughly square display 256 pixels wide by 192 lines high. It is capable of displaying 9 colors: black, green, yellow, blue, red, buff, cyan, magenta, and orange. It can generate a few modes: text modes, graphics modes, and "semigraphics" modes. The semigraphics modes replace each character position from a text mode with blocks containing pixels.

The CoCo is physically wired such that its default alphanumeric display is semigraphics-4 mode.

In alphanumeric mode, each character is a 5 dot wide by 7 dot high character in a box 8 dots wide and 12 lines high. This display mode consumes 512 bytes of memory and is a 32 character wide

screen with 16 lines. The internal ROM character generator only holds 64 characters, so no lower case characters are provided. Lower case is instead "simulated" by inverting the color of the character.

Semigraphics is a hybrid display mode where alphanumerics and block graphics can be mixed together on the same screen. See other sections for details.

By setting the SAM such that it believes it is displaying a full graphics mode, but leaving the VDG in Alphanumeric/Semigraphics 4 mode, it is possible to subdivide the character box into smaller pieces. This creates the "virtual" modes Semigraphics 8, 12, and 24. These modes were not implemented on the CoCo 3.

There were several full graphics display modes, -C (for "color) modes and -R (for "resolution") modes. See elsewhere in this document for details.

The 256x192 two-color mode allows "artifact colors" on an NTSC TV, due to limitations of the phase relationship between the VDG clock and colorburst signal. In the white and black colorset, alternating dots bleed together to give red or blue, in effect giving a 128x192 four color mode with red, black, white, and blue. Reversing dot order reverses artifact colors. However, the color formed is somewhat random on RESET, so many games have the player press RESET until the colors are correct for the game. The CoCo 3 fixed this problem, always starting the same, and holding F1 during reset would reverse the colors. Artifacting does not work on the RGB monitors.

Graphics modes are covered in the section on <u>Graphics Modes</u>.

The VDG is programmed through <u>PIA1</u>.

## SAM (Synchronous Address Multiplexer)

The <u>SAM</u> is a Motorola MC6883 or SN74LS785.

The SAM performs the following functions:

- Clock generation and synchronization for the 6809E CPU and 6847 VDG

- Up to 64K Dynamic Random Access Memory (DRAM) control and refresh

- Device selection based on CPU memory address to determine if the CPU access is to DRAM, ROM, PIA, etc.

- Duplication of the VDG address counter to "feed" the VDG the data it is expecting

- Divides the internal 4x NTSC freq (14.31818MHz for NTSC) by 4, passes it to the VDG for its own internal timing (3.579545MHz for NTSC).

- Divides the master clock by 16 (or 8 in certain cases) for the two phase CPU clock in NTSC this is .89MHz (or 1.8MHz if div by 8).

The SAM's 16-bit configuration register is spread across 32 memory addresses (<u>\$FFC0-\$FFDF</u>). Writing even addresses sets that register bit to 0; writing to odd addresses sets it to 1.

The SAM contains a duplicate of the VDG's 12-bit address counter, and usually is programmed to be in sync. Mixing modes between the two results in other possible modes.

There are actually three speed settings on the CoCo. The default is to run at .895 MHz all the time. There is another setting that makes it run at twice that speed when accessing the ROM memory, but still at the slower speed when accessing RAM, called "address dependent" or "AD". Finally, there is a speed setting that uses the double speed all the time.

When the CPU chip runs faster, it generates more heat. Most CoCo 6809's can take the heat of running double-speed, but some might burn out, so do it at your own risk, especially on older, early version CoCos.

Note that a lot of the timing-dependent things in the CoCo BASIC ROMs won't work right at any speed other than "slow", like reading or writing cassettes and disks, and making sounds. On CoCo 1 and 2 it also causes problems with the display.

Clock speed is controlled by addresses <u>\$FFD6-\$FFD9</u> in the SAM.

### TODO

# **Color Computer 3 Hardware Topics (GIME)**

The CoCo 3 supports the hardware of the CoCo 1 and 2, and adds a multifunction chip, the GIME. There were two versions, the 1986 and 1987 versions.

TODO – version differences? 256 color mode conjecture?

## GIME (Graphics Interrupt Memory Enhancement)

The <u>GIME</u> is a custom ASIC chip designed to replace and extend many parts in the original CoCo 1 and 2. The main features added are support for more than 64K of memory (128K was the standard, and a 512K upgrade was common), advanced graphics modes, and more interrupt options. A mode bit (bit 7) in <u>INITO</u> (\$FF90) (bit 7) switched between CoCo 1/2 mode and CoCo 3 mode.

There are many other features, covered in the hardware section for the GIME, which uses hardware registers <u>\$FF90-\$FFBF</u>. Here are a few features.

The GIME adds

- Many more graphics and text options.

- New interrupt sources, like timer and keyboard.

- Ability to address more memory (128K in original CoCo 3's, 512K after upgrade. There are other, bigger upgrades available). The Memory Management Unit (MMU, registers <u>\$FFA0-</u><u>\$FFAF</u>) handles this by paging 8K blocks into the address space used by the CPU

### **MMU (Memory Management Unit)**

The first thing to learn about the GIME is to understand the <u>MMU</u>, and how addresses from the GIME memory space map to the CPU memory space. The MMU is controlled by addresses <u>\$FFA0-\$FFAF</u>, and more details are under the section on <u>Memory Mapping</u>.

### Graphics

See the  $\underline{GIME}$  hardware section. TODO – table?

### Palettes

See the <u>GIME</u> hardware section on <u>Palettes (\$FFB0-\$FFBF)</u> and the <u>Colors</u> section. TODO – palettes?

### Interrupts

See the <u>GIME</u> hardware section on interrupts. TODO

## CoCo 1/2 compatibility

A mode bit (bit 7) in <u>INITO</u> (<u>\$FF90</u>) (bit 7) switched between CoCo 1/2 mode and CoCo 3 mode. To use CoCo 1/2 graphics modes, set this bit. To use CoCo 3 graphics modes, clear this bit.

## **Memory Mapping**

This section covers how memory is mapped into the CPU space on the CoCo 1, 2, and 3.

## CoCo 1/2:

32/64K maps see TODO TODO

## CoCo 2 memory map

| Address       | Usage                                                 |  |  |

|---------------|-------------------------------------------------------|--|--|

| \$0000-\$0069 | Direct Page RAM: available for M/L Programs           |  |  |

| \$006A-\$00FF | Internal Use                                          |  |  |

| \$006F        | DEVNUM: 0=screen, FE=printer                          |  |  |

| \$007D        | BLKLEN: number of bytes in a block (0-255)            |  |  |

| \$007C        | BLKTYP: block type: 0=header, 1=data, FF=end          |  |  |

| \$007E        | CBUFAD: buffer address (two bytes?)                   |  |  |

| \$0081        | CSRERR: cassette error code                           |  |  |

| \$0100-\$0111 | Interrupt Vectors                                     |  |  |

| \$0112-\$0114 | USRJMP - Jump to BASIC USR function                   |  |  |

| \$0115-\$0119 | Unassigned - available for M/L Programs               |  |  |

| \$011A        | Keyboard Alpha Lock ( $0 = not locked$ ; FF = Locked) |  |  |

| \$011B-\$011C | Keyboard Delay Constant                               |  |  |

| ¢011D ¢0151     |                                           |  |

|-----------------|-------------------------------------------|--|

| \$011D-\$0151   | Unassigned - available for M/L Programs   |  |

| \$0152-\$0159   | Keyboard Rollover Tables                  |  |

| \$015A-\$015D   | POTVAL: Joystick values                   |  |

|                 | \$15A Right joystick, left/right value    |  |

|                 | \$15B Right joystick, up/down value       |  |

|                 | \$15C Left joystick, left/right value     |  |

|                 | \$15D Left joystick, up/down value        |  |

| \$015E - \$03FF | Internal Use                              |  |

| \$0400-\$05FF   | Video Text memory                         |  |

| \$0600-\$1FFF   | User's BASIC program (4K RAM)             |  |

| \$0600-\$3FFF   | User's BASIC program (16K RAM)            |  |

| \$0600-\$7FFF   | User's BASIC program (32K or 64K RAM)     |  |

| \$8000-\$9FFF   | Extended Color BASIC ROM                  |  |

| \$A000-\$BFFF   | Color BASIC                               |  |

| \$C000-\$DFFF   | Cartridge ROM Space                       |  |

| \$E000-\$FEFF   | Unused                                    |  |

| \$FF00-\$FFFF   | I/O, machine configuration, reset vectors |  |

## CoCo 3

The GIME chip can access 512K of memory, yet the 6809 CPU can only access 64K. The barrier is broken by a MMU (Memory Management Unit) that splits the access into 8 blocks visible to the CPU of 8K each.

To use the memory mapping, bit 6 of <u>INIT0</u> (<u>\$FF90</u>) must be set to 1,

There are two possible memory maps, Map 0 and Map 1, selected by bit 0 of the <u>INIT1</u> (<u>\$FF91</u>) register. Setting this bit to 0 enables Map 0 (using the pages stored in \$FFA0-\$FFA7), and setting this bit to 1 enables Map 1 (using pages in \$FFA8-\$FFAF).

TODO see <a href="http://www.coco25.com/wiki/index.php/MMU\_RAMROM\_Mode">http://www.coco25.com/wiki/index.php/MMU\_RAMROM\_Mode</a>

A memory page is an 8K block in the GIME address space. A 128K system has 128/8=16 blocks, numbered hex \$30-\$3F. A 512K system has 64 blocks, numbered hex \$00-\$3F. To place a page in CPU memory for access, write the page number in the appropriate memory select register.

In RAM/ROM mode, the ROM pages (\$3C-\$3F) can be written to any of the eight available MMU slots. In all cases the last two bits of the page are ignored by the MMU and substituted by the last two bits of the slot number. This might cause some addressing confusion, and should be noted.

A memory page number is a 6-bit value. When reading the memory select registers, be sure to mask off the top two bits, since they can contain garbage.

The memory select registers are registers <u>\$FFA0-\$FFAF</u>. A write of a page value to the address on the left makes the page visible at the CPU address on the right.

| Map 0 | Map 1 |

|-------|-------|

|       |       |

| \$FFA0 -> \$0000-\$1FFF | \$FFA8 -> \$0000-\$1FFF |

|-------------------------|-------------------------|

| \$FFA1 -> \$2000-\$2FFF | \$FFA9 -> \$2000-\$2FFF |

| \$FFA2 -> \$4000-\$5FFF | \$FFAA -> \$4000-\$5FFF |

| \$FFA3 -> \$6000-\$7FFF | \$FFAB -> \$6000-\$7FFF |

| \$FFA4 -> \$8000-\$9FFF | \$FFAC -> \$8000-\$9FFF |

| \$FFA5 -> \$A000-\$BFFF | \$FFAD -> \$A000-\$BFFF |

| \$FFA6 -> \$C000-\$DFFF | \$FFAE -> \$C000-\$DFFF |

| \$FFA7 -> \$E000-\$FFFF | \$FFAF -> \$E000-\$FFFF |

Details are in the hardware reference for the MMU.

Example: to set GIME memory location \$60000 to value 0, you could:

| ORCC | #\$50  | SHUT OFF INTERRUPTS - TODO - SAVE FOR RESTORE LATER |

|------|--------|-----------------------------------------------------|

| LDA  | \$FFA1 | GET THE PAGE FOR THE RESTORE                        |

| ANDA | #63    | STRIP OFF TOP BITS                                  |

| PSHS | A      | SAVE THE PAGE FOR LATER                             |

| LDA  | #\$30  | ACCESS TO PAGE \$30 = GIME \$60000                  |

| STA  | \$FFA1 | MAP PAGE \$60000-\$61FFF TO LOCATIONS \$2000-\$3FFF |

| LDA  | #\$00  | THE BYTE IS 0                                       |

| STA  | \$2000 | SET THE PROPER BYTE IN CPU SPACE                    |

| PULS | A      | RESTORE THE PAGE VALUE THAT WAS THERE               |

| STA  | \$FFA1 | MAP ORIGINAL PAGE BACK INTO CPU SPACE               |

Notes:

- 1. Unless you know what you are doing, shut off interrupts when changing pages. If you change a page that has an interrupt handler in it, and an interrupt occurs, you will likely crash the computer.

- 2. If you are using the stack, be careful if you page out the stack. Return addresses may be changed, and stack values will not likely be the same. Therefore, KNOW WHERE THE STACK IS! In basic, it starts in the \$6000-\$7FFF page.

### Simple CoCo 3 Memory Map

Here is a simple CoCo 3 memory map. Detailed versions are in the section on <u>Detailed Memory</u> <u>Maps</u>.

| Page  | GIME Address    | CPU Address | Standard Page Contents                 |

|-------|-----------------|-------------|----------------------------------------|

| \$00- | 00000-\$5FFFF   |             | 512K upgrade RAM, unused by BASIC; not |

| 2F    |                 |             | present in 128K or smaller systems     |

| \$30  | \$60000-\$61FFF |             | Hi-Res page #1                         |

| \$31  | \$62000-\$63FFF |             | Hi-Res page #2                         |

| \$32  | \$64000-\$65FFF |             | Hi-Res page #3                         |

| \$33  | \$66000-\$67FFF |             | Hi-Res page #4                         |

| \$34  | \$68000-\$69FFF |             | HGET/HPUT buffer                       |

| \$35  | \$6A000-\$6BFFF |             | Secondary Stack                        |

| \$36  | \$6C000-\$6DFFF |             | Hi-Res text screen RAM                 |

Here are page values for GIME address, default page values on a power up, and default CPU addresses:

| \$37 | \$6E000-\$6FFFF |               | Unused by BASIC                         |

|------|-----------------|---------------|-----------------------------------------|

| \$38 | \$70000-\$71FFF | \$0000-\$1FFF | BASIC memory                            |

| \$39 | \$72000-\$73FFF | \$2000-\$3FFF | BASIC memory                            |

| \$3A | \$74000-\$75FFF | \$4000-\$5FFF | BASIC memory                            |

| \$3B | \$76000-\$77FFF | \$6000-\$7FFF | BASIC memory                            |

| \$3C | \$78000-\$79FFF | \$8000-\$9FFF | Extended Basic ROM                      |

| \$3D | \$7A000-\$7BFFF | \$A000-\$BFFF | Color Basic ROM                         |

| \$3E | \$7C000-\$7DFFF | \$C000-\$DFFF | Cartridge or Disk Basic ROM             |

| \$3F | \$7E000-\$7FFFF | \$D000-\$FFFF | Super Basic, GIME regs, I/O, Interrupts |

A little more detail for the default power on situation for the BASIC memory sections, and \*CIME Address\* \*Contents\*

| *Contents*                                                |

|-----------------------------------------------------------|

| System RAM                                                |

| Lowres text screen                                        |

| \$                                                        |

| Page 1 - lowres graphics                                  |

| Page 2                                                    |

| Page 3                                                    |

| Page 4                                                    |

| Page 5                                                    |

| Page 6                                                    |

| Page 7                                                    |

| Page 8                                                    |

|                                                           |

| Disk System RAM                                           |

|                                                           |

| 1 - 8 graphic pages reserved, Basic program start varies. |

|                                                           |

| programs, variables, and user ml programs                 |

|                                                           |

|                                                           |

|                                                           |

| Super Extended Basic                                      |

| Secondary vector table                                    |

| PIAs                                                      |

| GIME in CoCo 3                                            |

| video control, clock, and map type                        |

| Unused                                                    |

| Interrupt vectors                                         |

|                                                           |

Note: the Vector Page RAM at \$7FE00 - \$7FEFF (when enabled), will appear instead of the RAM or ROM at \$FE00 - \$FEFF. (see INITO (\$FF90) Bit 3) TODO

The 256 top bytes \$FF00-\$FFFF in CPU space contain byte-mapped hardware interfaces, covered elsewhere in this doc.

TODO - make sure all this in detailed maps

TODO - Merge memory maps into one section, with two or three levels of detail.

## Colors

### CoCo 1/2:

### TODO

## CoCo 3:

Palette colors are defined in registers <u>\$FFB0-\$FFBF</u>. The format differs depending on if you are in RGB or Composite monitor mode. Mode is selected by setting TODO

Default composite colors on startup:

|        | 1       |    | 1      |        |    |

|--------|---------|----|--------|--------|----|

| \$FFB0 | GREEN   | 18 | \$FFB8 | BLACK  | 00 |

| \$FFB1 | YELLOW  | 36 | \$FFB9 | GREEN  | 18 |

| \$FFB2 | BLUE    | 11 | \$FFBA | BLACK  | 00 |

| \$FFB3 | RED     | 07 | \$FFBB | BUFF   | 63 |

| \$FFB4 | BUFF    | 63 | \$FFBC | BLACK  | 00 |

| \$FFB5 | CYAN    | 31 | \$FFBD | GREEN  | 18 |

| \$FFB6 | MAGENTA | 09 | \$FFBE | BLACK  | 00 |

| \$FFB7 | ORANGE  | 38 | \$FFBF | ORANGE | 38 |

|        |         |    |        |        |    |

Entering PALETTE CMP or PALETTE RGB will set this palette for the type of monitor you are using.

The format is explained in the GIME Palette (<u>\$FFB0-\$FFBF</u>) register section.

The table of (hex) colors given below is the conversion used in OS-9 Level II.

| Moni | tor C | olor                   | Moni | tor C | olor                     |

|------|-------|------------------------|------|-------|--------------------------|

| RGB  | CMP   |                        | RGB  | CMP   |                          |

| 00   | 00    | Black                  | 32   | 23    | Medium intensity red     |

| 01   | 12    | Low intensity blue     | 33   | 08    | Blue tint red            |

| 02   | 02    | Low intensity green    | 34   | 21    | Light Orange             |

| 03   | 14    | Low intensity cyan     | 35   | 06    | Cyan tint red            |

| 04   | 07    | Low intensity red      | 36   | 39    | Full intensity red       |

| 05   | 09    | Low intensity magenta  | 37   | 24    | Magenta tint red         |

| 06   | 05    | Low intensity brown    | 38   | 38    | Brown tint red           |

| 07   | 16    | Low intensity white    | 39   | 54    | Faded red                |

| 08   | 28    | Medium intensity blue  | 40   | 25    | Medium intensity magenta |

| 09   | 44    | Full intensity blue    | 41   | 42    | Blue tint magenta        |

| 10   | 13    | Green tint blue        | 42   | 26    | Green tint magenta       |

| 11   | 29    | Cyan tint blue         | 43   | 58    | Cyan tint magenta        |

| 12   | 11    | Red tint blue          | 44   | 24    | Red tint magenta         |

| 13   | 27    | Magenta tint blue      | 45   | 41    | Full intensity magenta   |

| 14   | 10    | Brown tint blue        | 46   | 40    | Brown tint magenta       |

| 15   | 43    | Faded blue             | 47   | 56    | Faded magenta            |

| 16   | 34    | Medium intensity green | 48   | 20    | Medium intensity yellow  |

| 17   | 17    | Blue tint green        | 49   | 04    | Blue tint yellow         |

| 18 | 18 | Full intensity green  | 50 | 35 | Green tint yellow      |

|----|----|-----------------------|----|----|------------------------|

| 19 | 33 | Cyan tint green       | 51 | 51 | Cyan tint yellow       |

| 20 | 03 | Red tint green        | 52 | 37 | Red tint yellow        |

| 21 | 01 | Magenta tint green    | 53 | 53 | Magenta tint yellow    |

| 22 | 19 | Brown tint green      | 54 | 36 | Full intensity yellow  |

| 23 | 50 | Faded green           | 55 | 52 | Faded yellow           |

| 24 | 30 | Medium intensity cyan | 56 | 32 | Medium intensity white |

| 25 | 45 | Blue tint cyan        | 57 | 59 | Light blue             |

| 26 | 31 | Green tint cyan       | 58 | 49 | Light green            |

| 27 | 46 | Full intensity cyan   | 59 | 62 | Light cyan             |

| 28 | 15 | Red tint cyan         | 60 | 55 | Light red              |

| 29 | 60 | Magenta tint cyan     | 61 | 57 | Light magenta          |

| 30 | 47 | Brown tint cyan       | 62 | 63 | Light yellow           |

| 31 | 61 | Faded cyan            | 63 | 48 | White                  |

TODO – there is a dup in the entries – check elsewhere, and also make reverse table. 24 is used twice in the CMP side, and 22 is missed on the CMP side.

## **Graphics Modes**

## CoCo 1/2

TODO - table? From http://homepage.ntlworld.com/kryten\_droid/coco/coco\_tm\_s3.htm ?

TODO - add semigraphics 8, 12, and 24 modes info?

ALPHANUMERIC DISPLAY MODES – All alphanumeric modes occupy an 8 x 12 dot character matrix box and there are 32 x 16 character boxes per TV frame. Each horizontal dot (dot-clock) corresponds to one half the period duration of the 3.58 MHz clock and each vertical dot is one scan line. One of two colors for the lighted dots may be selected by the color set select pin (pin 39). An internal ROM will generate 64 ASCII display characters in a standard 5 x 7 box. Six bits of the eight-bit data word are used for the ASCII character generator and the two bits not used are used to implement inverse video and mode switching to semigraphics – 4, – 8, – 12, or – 24.

The ALPHA SEMIGRAPHICS – 4 mode translates bits 0 through 3 into a 4 x 6 dot element in the standard 8 x 12 dot box. Three data bits may be used to select one of eight colors for the entire character box. The extra bit is used to switch to alphanumeric. A 512 byte display memory is required. A density of 64 x 32 elements is available in the display area. The element area is four dot-clocks wide by six lines high.

The ALPHA SEMIGRAPHICS - 6 mode maps six 4 x 4 dot elements into the standard 8 x 12 dot alphanumeric box, a screen density of 64 x 48 elements is available. Six bits are used to generate this map and two data bits may be used to select one of four colors in the display box. A 512 byte display memory is required. The element area is four dot-clocks wide by four lines high.

The ALPHA SEMIGRAPHICS -8 mode maps eight 4 x 3 dot elements into the standard 8 x 12 dot box. This mode requires four memory locations per box and each memory location may specify one of eight colors or black. A 2048 byte display memory is required. A density of 64 x 64

elements is available in the display area. The element area is four dot-clocks wide by three lines high.

The ALPHA SEMIGRAPHICS – 12 mode maps twelve 4 x 2 dot elements into the standard 8 x 12 dot box. This mode requires six memory locations per box and each memory location may specify one of eight colors or black. A 3072 byte display memory is required. A density of 64 x 96 elements is available in the display area. The element area is four dot-clocks wide by two lines high.

The ALPHA SEMIGRAPHICS – 24 mode maps twenty-four 4 x 1 dot elements into the standard 8 x 12 dot box. This mode requires twelve memory locations per box and each memory location may specify one of eight colors or black. A 6144 byte display memory is required. A density of 64 x 192 elements is available in the display are. The element area is four dot-clocks wide by one line high.

FULL GRAPHIC MODES – There are eight full graphic modes available from the VDG. These modes require 1K to 6K bytes of memory. The eight full-graphic modes include an outside color border in one of two colors depending upon the color set select pin (CSS). The CSS pin (pin 39) selects one of two sets of four colors in the four color graphic modes.

The 64 x 64 Color Graphics mode generates a display matrix of 64 elements wide by 64 elements high. Each element may be one of four colors. A 1K x 8 display memory is required. Each pixel equals four dot-clocks by three scan lines.

The 128 x 64 Graphics Mode generates a matrix 128 elements wide by 64 elements high. Each element may be either ON or OFF. However, the entire display may be one of two colors, selected by using the color set select pin. A 1K x 8 display memory is required. Each pixel equals two dot-clocks by three scan lines.

The 128 x 64 Color Graphics mode generates a display matrix 128 elements wide by 64 elements high. Each element may be one of four colors. A 2K x 8 display memory is required. Each pixel equals two dot-clocks by three scan lines.

The 128 x 96 Graphics mode generates a display matrix 128 elements wide by 96 elements high. Each element may be either ON or OFF. However, the entire display may be one of two colors selected by using the color select pin. A 2K x 8 display memory is required. Each pixel equals two dot-clocks by two scan lines.

The 128 x 96 Color Graphics mode generates a display 128 elements wide by 96 elements high. Each element may be one of four colors. A 3K x 8 display memory is required. Each pixel equals two dot-clocks by two scan lines.

The 128 x 192 Graphics mode generates a display matrix 128 elements wide by 192 elements high. Each element may be either ON or OFF, but the ON elements may be one of two colors selected with color set select pin. A 3K x 8 display memory is required. Each pixel equals two dot-clocks by one scan line.

The 128 x 192 Color Graphics mode generates a display 128 elements wide by 192 elements high. Each element may be one of four colors. A  $6K \ge 8$  display memory is required. A detailed description of the VDG modes is given in Table 2. Each pixel equals two dot-clocks by one scan line.

The 256 x 192 Graphics mode generates a display 256 elements wide by 192 elements high. Each element may be either ON or OFF, but the ON element may be one of two colors selected with the color set select pin. A 6K x 8 display memory is required. Each pixel equals one dot-clock by one scan line.

|     | /DG<br>INS |                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | T              | VSCREEN                                                                        |                                                                                                                                                                                                      |                                                        |                                                                                                                                                                                                                                                                                                                                                                     |

|-----|------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CSS | S IN       |                                                     | Character Color Backgroun                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Border         | Display Mode                                                                   | Detail                                                                                                                                                                                               | VDG DATA BUS                                           | COMMENTS                                                                                                                                                                                                                                                                                                                                                            |

| 0   | 0          |                                                     | Green Black<br>Black Green<br>Orange Black<br>Black Oranne                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Black<br>Black | 32 Characters<br>in columns<br>16 Characters                                   | 8 dots  <br>12 dots 7                                                                                                                                                                                | 0 N                                                    | The ALPHANUMERIC INTERNAL mode uses an internal character generator which contains the following five dot by seven dot characters:<br>@ A B C D E F G H J K L M N O P O R S T U V W X Y Z / / 1                                                                                                                                                                     |

| x   | ×          | 1                                                   | Black         Orange           0         2         21         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00 <td< th=""><th>Black</th><th>in rows<br/>64 Display elements<br/>in columns<br/>32 Display elements<br/>in rows</th><th>L<sub>3</sub> L<sub>2</sub><br/>L<sub>1</sub> L<sub>0</sub> one element</th><th>ASCII code</th><th>The SEMIGRAPHICS FOUR mode uses an internal "coarse<br/>graphics" generator in which a rectangle (eight dots by twelve<br/>dots) is divided into four equal parts. The luminance of each<br/>part is determined by a corresponding bit on the VOG data<br/>bus. The color of Illuminated parts is determined by three bits.<br/>It requires 512 bytes of display memory.</th></td<> | Black          | in rows<br>64 Display elements<br>in columns<br>32 Display elements<br>in rows | L <sub>3</sub> L <sub>2</sub><br>L <sub>1</sub> L <sub>0</sub> one element                                                                                                                           | ASCII code                                             | The SEMIGRAPHICS FOUR mode uses an internal "coarse<br>graphics" generator in which a rectangle (eight dots by twelve<br>dots) is divided into four equal parts. The luminance of each<br>part is determined by a corresponding bit on the VOG data<br>bus. The color of Illuminated parts is determined by three bits.<br>It requires 512 bytes of display memory. |

| ø   | ×          |                                                     | Lx C1 C0 Color<br>0 X X Black<br>1 0 0 Green<br>1 0 1 Green<br>1 0 Blue<br>1 1 Red                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Black          | 64 Display elements<br>in columns                                              | L <sub>5</sub> L <sub>4</sub><br>L <sub>3</sub> L <sub>2</sub>                                                                                                                                       | C1 C0 L5 L4 L3 L2 L1 L0                                | The SEMIGRAPHIC SIX mode is similar to the SEMIGRAPHIC FOUR mode with the following difference: The eight dot by                                                                                                                                                                                                                                                    |

| 1   |            | ,                                                   | Ø         X         X         Black           1         Ø         Ø Buff           1         Ø         Buff           1         Ø         Buff           1         1         Ø Magenta           1         1         Ø Orange                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                | 48 Display elements<br>in rows                                                 |                                                                                                                                                                                                      |                                                        | twelve dot rectangle is divided into six equal parts. Color is<br>determined by the two remaining bits. It requires 512 bytes of<br>display memory.                                                                                                                                                                                                                 |

| x   | x          |                                                     | X         C2         C1         CØ         Color           Ø         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Black          | 64 Display elements<br>in columns<br>64 Display elements<br>in rows            | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                               | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$  | The SEMIGRAPHIC EIGHT mode requires four column<br>consecutive addresses*, and produces a 2 x 4 block. It requires<br>2048 bytes of display memory.                                                                                                                                                                                                                 |

| ×   | x          | Ø<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | x C2 C1 CØ Color                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Black          | 64 Display elements<br>in columns<br>96 Display elements<br>in rows            | L <sub>1</sub> L <sub>0</sub><br>L <sub>3</sub> L <sub>2</sub><br>L <sub>5</sub> L <sub>4</sub><br>L <sub>7</sub> L <sub>6</sub><br>L <sub>9</sub> L <sub>8</sub><br>L <sub>11</sub> L <sub>10</sub> | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | The SEMIGRAPHIC TWELVE mode requires six column<br>consecutive addresses <sup>*</sup> , and produces a 2 x 6 block. It requires<br>3072 bytes of display memory.                                                                                                                                                                                                    |

|     |            |                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                |                                                                                |                                                                                                                                                                                                      |                                                        |                                                                                                                                                                                                                                                                                                                                                                     |

25

\*Four column consecutive addresses starting at HEX Ø400 are Ø400, Ø420, Ø440, Ø460.

17

|     | DG<br>NS         |                                                                                                                                                                                                                                                                                            | cc                                                     | DLOR                                                                         |                                                       | тv                                                                                                                                                                                                                                                                                                   | SCREEN                                                                                                                                                       | VDG DATA BUS                                                   | COMMENTS                                                                                                                             |

|-----|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| css | IN               | 1.0                                                                                                                                                                                                                                                                                        | Character Color                                        | Background                                                                   | Border                                                | Display Mode                                                                                                                                                                                                                                                                                         | Detail                                                                                                                                                       |                                                                |                                                                                                                                      |

| ×   | . ,              | 1         0         0         G reen         ir           1         0         0         1         Yellow         ir           X         1         0         1         Yellow         Black         122 L           1         0         1         1         Red         192 L         192 L |                                                        | 64 Display elements<br>in columns<br>192 Display elements<br>in rows         | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c c} 1 & C_2 C_1 C_0 & L_1 L_0 \times \\ \hline 1 & C_2 C_1 & C_0 & L_3 L_2 \times \\ \hline 1 & C_2 C_1 C_0 & L_5 L_4 \times \\ \hline 1 & C_2 C_1 C_0 & L_5 L_4 \times \\ \hline 1 & C_2 C_1 C_0 & L_7 L_6 \times \\ \hline 1 & C_2 C_1 C_0 & L_9 L_8 \times \\ \hline \end{array}$ | The SEMIGRAPHIC TWENTY FOUR mode requires twelve<br>column consecutive addresses*, and produces a 2 x 12 block.<br>It requires 6144 bytes of display memory. |                                                                |                                                                                                                                      |

|     |                  |                                                                                                                                                                                                                                                                                            |                                                        |                                                                              |                                                       |                                                                                                                                                                                                                                                                                                      | $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                       | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$         |                                                                                                                                      |

| 0   | <b>-</b> x       |                                                                                                                                                                                                                                                                                            | C1 C9<br>9 9<br>1 1<br>1 1<br>9 9<br>1 1<br>1 9<br>1 9 | Color<br>Green<br>Yellow<br>Blue<br>Red<br>Buff<br>Cyan<br>Magenta<br>Orange | Green<br>Buff                                         | 64 Display elements<br>in columns<br>64 Display elements<br>in rows                                                                                                                                                                                                                                  | E <sub>3</sub> E <sub>2</sub> E <sub>1</sub> E <sub>0</sub>                                                                                                  | C1C0C1C0C1C0C1C0                                               | The GRAPHICS ONE C mode uses a maximum of 1024 bytes<br>of display RAM in which one pair of bits specifies one picture<br>element.   |